基于FPGA的64bits算术乘法器设计Verilog代码Quartus仿真

温馨提示:这篇文章已超过399天没有更新,请注意相关的内容是否还可用!

名称:基于FPGA的64bits算术乘法器设计Verilog代码Quartus仿真(文末获取)

软件:Quartus

语言:Verilog

代码功能:

设计64bits算术乘法器

基本功能:

1.用 Veriloghdl设计实现64bit二进制整数乘法器,底层乘法器使用16*16\8*8\8*32\8*16

小位宽乘法器来实现,底层乘法器可以使用FPGA内部IP实现;

2.基于 modelsim仿真软件对电路进行功能验证;

3.基于 Quartus平台对代码进行综合及综合后仿真,芯片型号不限

4.电路综合后的工作频率不低于50MHz。

报告要求

1.撰写设计方案,方案清晰合理;

2.提交 Veriloghdl设计代码,代码具有可综合性;

3.分别给出综合前后的仿真结果,并对比分析;

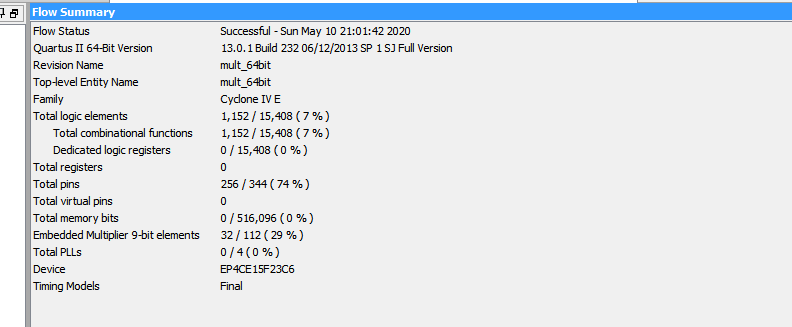

4.给出综合后电路的硬件资源及性能(如工作速度)等相关数据,简要分析资源和性能之间的关联性。

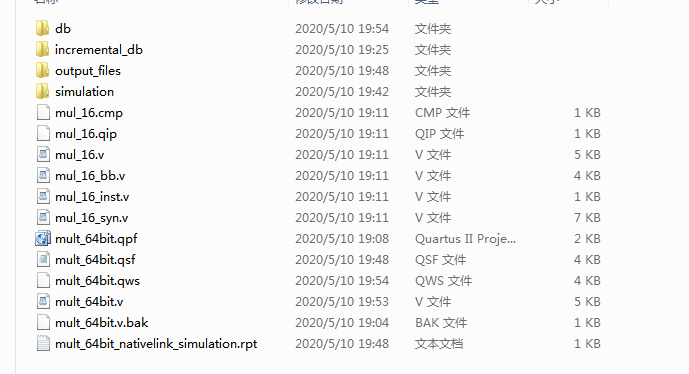

1. 工程文件

2. 程序文件

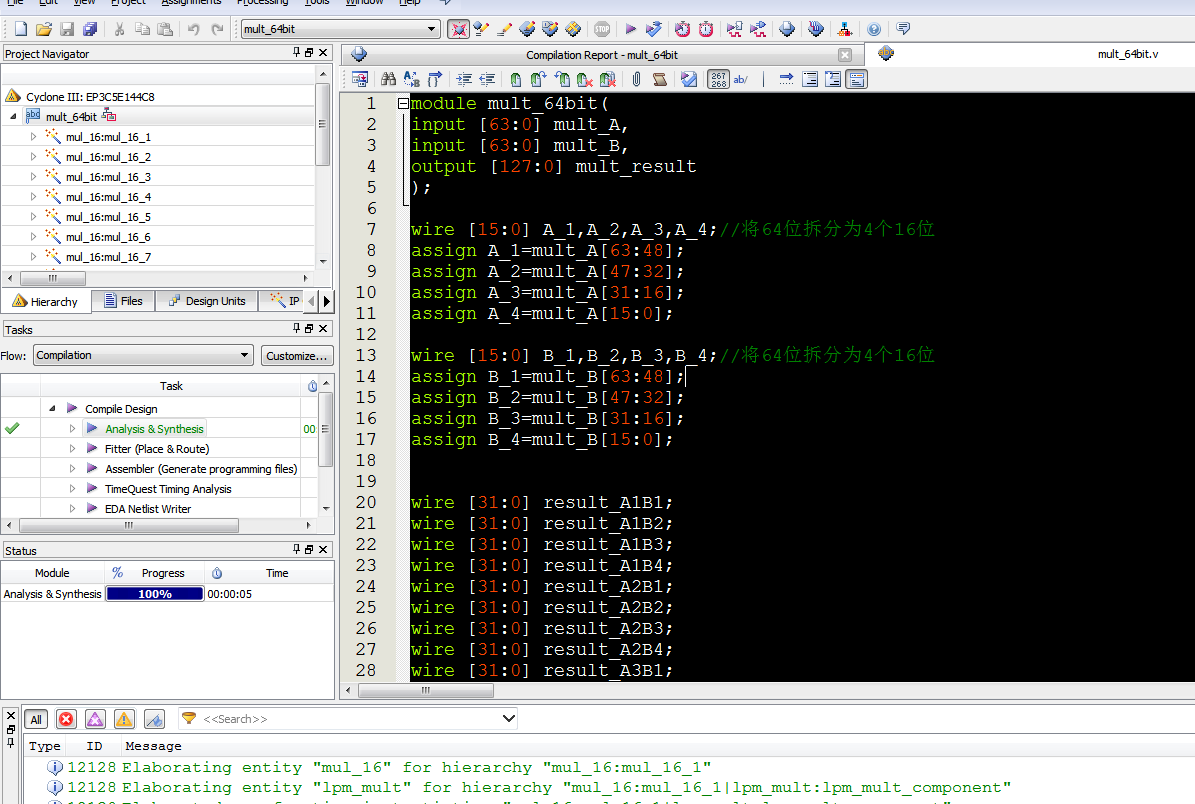

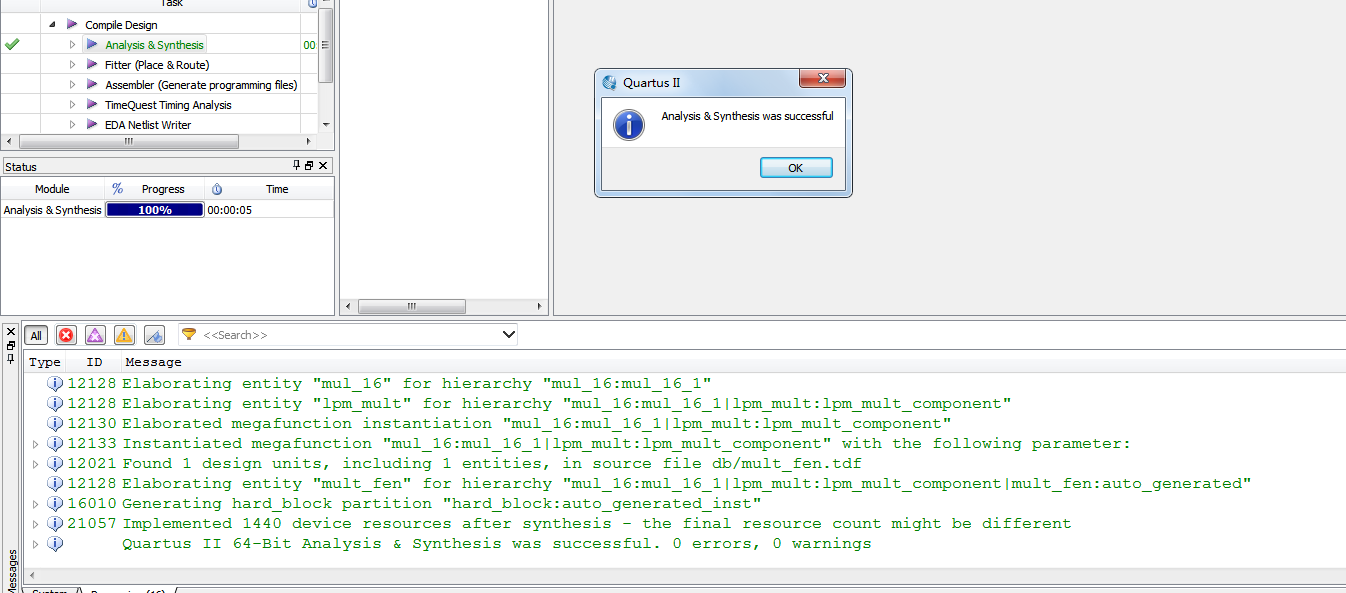

3. 程序编译

4. RTL图

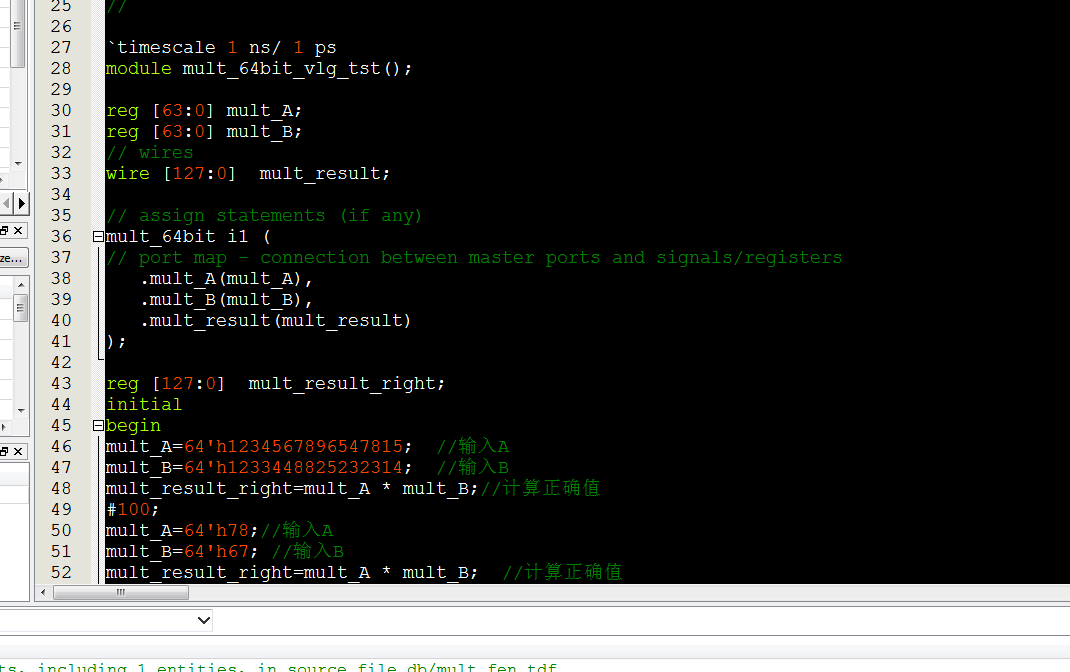

5. Testbench

6. 仿真图

可以看到,乘积正确

综合后仿真

部分代码展示:

// megafunction wizard: %LPM_MULT%VBB% // GENERATION: STANDARD // VERSION: WM1.0 // MODULE: lpm_mult // ============================================================ // File Name: mul_16.v // Megafunction Name(s): // lpm_mult // // Simulation Library Files(s): // lpm // ============================================================ // ************************************************************ // THIS IS A WIZARD-GENERATED FILE. DO NOT EDIT THIS FILE! // // 13.0.1 Build 232 06/12/2013 SP 1 SJ Full Version // ************************************************************ //Copyright (C) 1991-2013 Altera Corporation //Your use of Altera Corporation's design tools, logic functions //and other software and tools, and its AMPP partner logic //functions, and any output files from any of the foregoing //(including device programming or simulation files), and any //associated documentation or information are expressly subject //to the terms and conditions of the Altera Program License //Subscription Agreement, Altera MegaCore Function License //Agreement, or other applicable license agreement, including, //without limitation, that your use is for the sole purpose of //programming logic devices manufactured by Altera and sold by //Altera or its authorized distributors. Please refer to the //applicable agreement for further details. module mul_16 ( dataa, datab, result); input[15:0] dataa; input[15:0] datab; output[31:0] result; endmodule // ============================================================ // CNX file retrieval info // ============================================================ // Retrieval info: PRIVATE: AutoSizeResult NUMERIC "1" // Retrieval info: PRIVATE: B_isConstant NUMERIC "0" // Retrieval info: PRIVATE: ConstantB NUMERIC "0" // Retrieval info: PRIVATE: INTENDED_DEVICE_FAMILY STRING "Cyclone III" // Retrieval info: PRIVATE: LPM_PIPELINE NUMERIC "0" // Retrieval info: PRIVATE: Latency NUMERIC "0" // Retrieval info: PRIVATE: SYNTH_WRAPPER_GEN_POSTFIX STRING "1" // Retrieval info: PRIVATE: SignedMult NUMERIC "0" // Retrieval info: PRIVATE: USE_MULT NUMERIC "1" // Retrieval info: PRIVATE: ValidConstant NUMERIC "0" // Retrieval info: PRIVATE: WidthA NUMERIC "16" // Retrieval info: PRIVATE: WidthB NUMERIC "16" // Retrieval info: PRIVATE: WidthP NUMERIC "32" // Retrieval info: PRIVATE: aclr NUMERIC "0" // Retrieval info: PRIVATE: clken NUMERIC "0" // Retrieval info: PRIVATE: new_diagram STRING "1" // Retrieval info: PRIVATE: optimize NUMERIC "0" // Retrieval info: LIBRARY: lpm lpm.lpm_components.all // Retrieval info: CONSTANT: LPM_HINT STRING "MAXIMIZE_SPEED=5" // Retrieval info: CONSTANT: LPM_REPRESENTATION STRING "UNSIGNED" // Retrieval info: CONSTANT: LPM_TYPE STRING "LPM_MULT" // Retrieval info: CONSTANT: LPM_WIDTHA NUMERIC "16" // Retrieval info: CONSTANT: LPM_WIDTHB NUMERIC "16" // Retrieval info: CONSTANT: LPM_WIDTHP NUMERIC "32" // Retrieval info: USED_PORT: dataa 0 0 16 0 INPUT NODEFVAL "dataa[15..0]" // Retrieval info: USED_PORT: datab 0 0 16 0 INPUT NODEFVAL "datab[15..0]" // Retrieval info: USED_PORT: result 0 0 32 0 OUTPUT NODEFVAL "result[31..0]" // Retrieval info: CONNECT: @dataa 0 0 16 0 dataa 0 0 16 0 // Retrieval info: CONNECT: @datab 0 0 16 0 datab 0 0 16 0 // Retrieval info: CONNECT: result 0 0 32 0 @result 0 0 32 0 // Retrieval info: GEN_FILE: TYPE_NORMAL mul_16.v TRUE // Retrieval info: GEN_FILE: TYPE_NORMAL mul_16.inc FALSE // Retrieval info: GEN_FILE: TYPE_NORMAL mul_16.cmp TRUE // Retrieval info: GEN_FILE: TYPE_NORMAL mul_16.bsf FALSE // Retrieval info: GEN_FILE: TYPE_NORMAL mul_16_inst.v TRUE // Retrieval info: GEN_FILE: TYPE_NORMAL mul_16_bb.v TRUE // Retrieval info: GEN_FILE: TYPE_NORMAL mul_16_syn.v TRUE // Retrieval info: LIB_FILE: lpm

源代码

扫描文章末尾的公众号二维码

免责声明:我们致力于保护作者版权,注重分享,被刊用文章因无法核实真实出处,未能及时与作者取得联系,或有版权异议的,请联系管理员,我们会立即处理! 部分文章是来自自研大数据AI进行生成,内容摘自(百度百科,百度知道,头条百科,中国民法典,刑法,牛津词典,新华词典,汉语词典,国家院校,科普平台)等数据,内容仅供学习参考,不准确地方联系删除处理! 图片声明:本站部分配图来自人工智能系统AI生成,觅知网授权图片,PxHere摄影无版权图库和百度,360,搜狗等多加搜索引擎自动关键词搜索配图,如有侵权的图片,请第一时间联系我们,邮箱:ciyunidc@ciyunshuju.com。本站只作为美观性配图使用,无任何非法侵犯第三方意图,一切解释权归图片著作权方,本站不承担任何责任。如有恶意碰瓷者,必当奉陪到底严惩不贷!