7-20FPGA调试日志

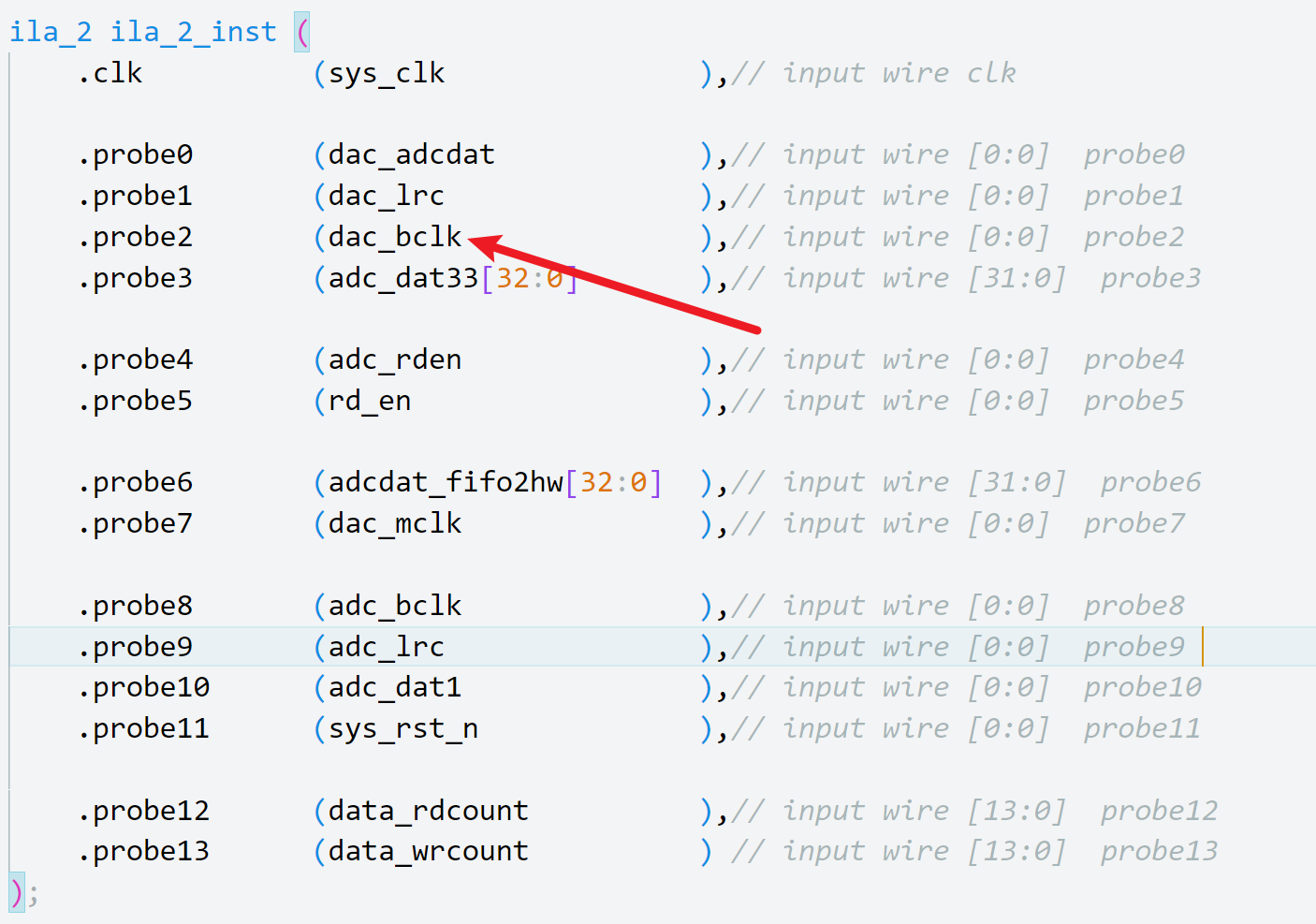

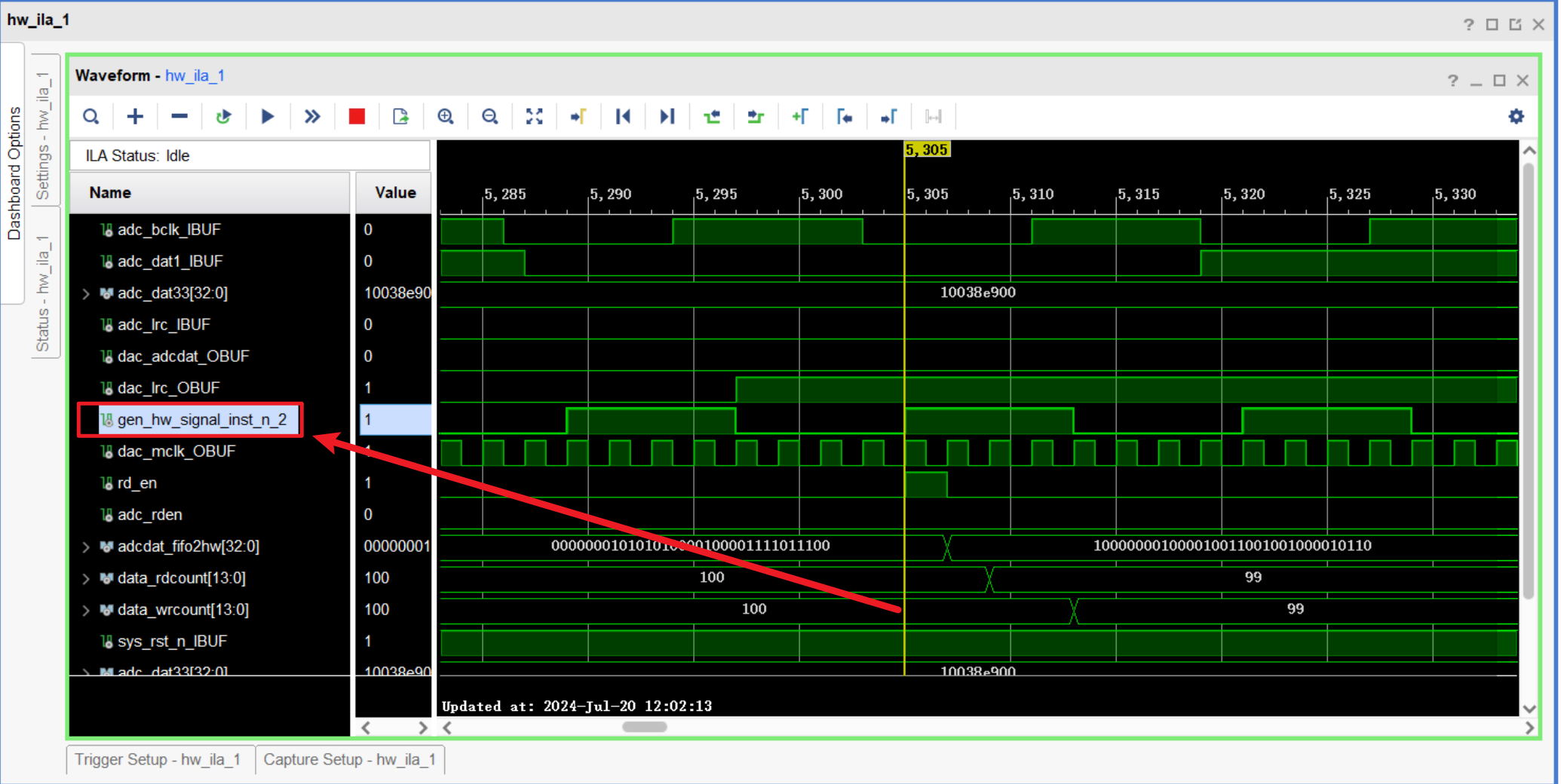

1. 在代码里面定义的ILA的变量名称与波形抓取界面的不一致

2. 直接从其他的播放声音的平台放音乐没问题,但是从AU里面生成的2kHz的正弦波放不出声音

演示视频链接

- 好像和ILA的例化信号有关,例化ILA信号的驱动时钟信号频率没有内部的其他信号的频率高

- 我把ila例化模块去掉后,AU播放的2kHz的正弦波也能正常播放

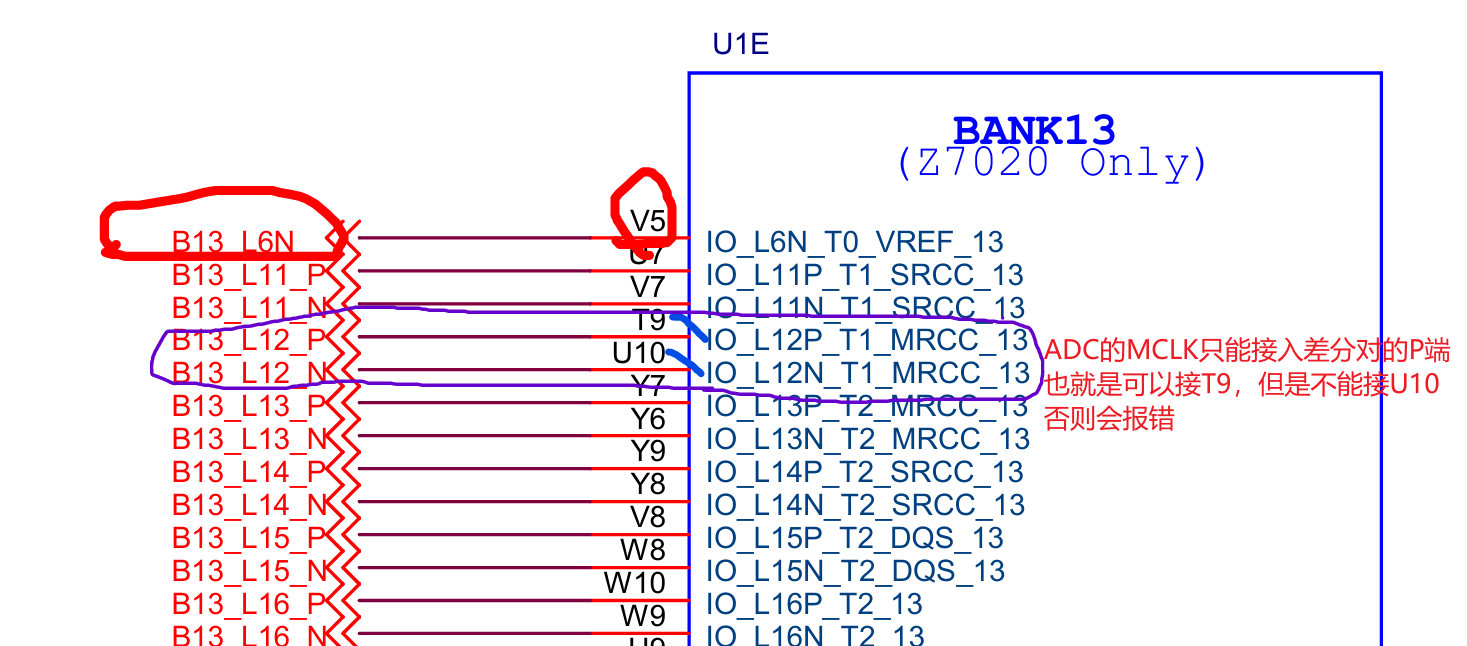

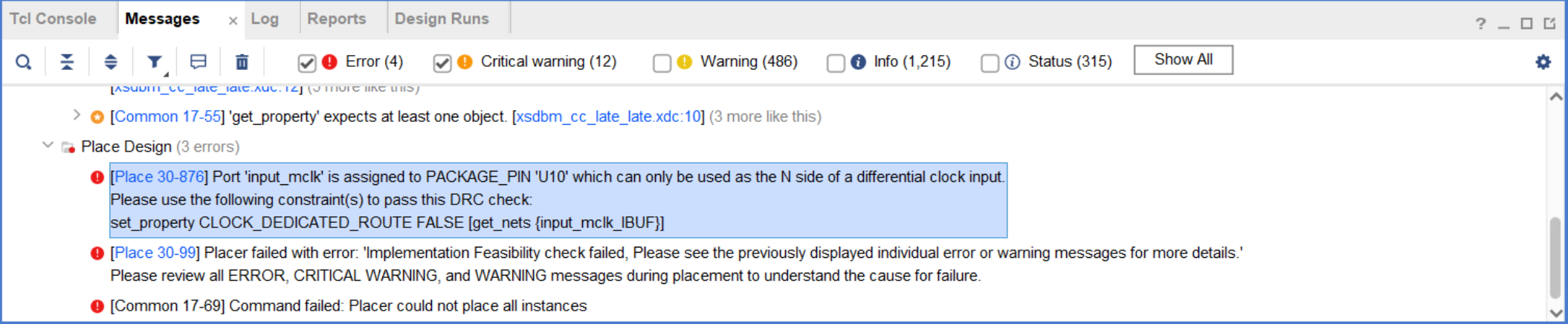

3. input_mclk(从音频ADC引入FPGA的引脚)只能绑定时钟专用引脚的同向端(P端),不能使用反向端(N端),否则会报错,不知道为什么

:::

修改到T9就正常了

对于输入FPGA的时钟信号,要从FPGA的时钟资源分配的引脚传入FPGA

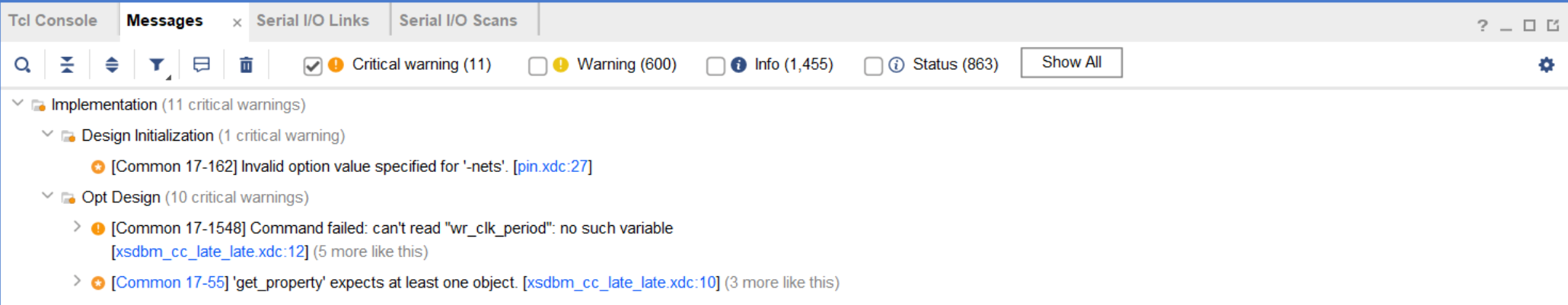

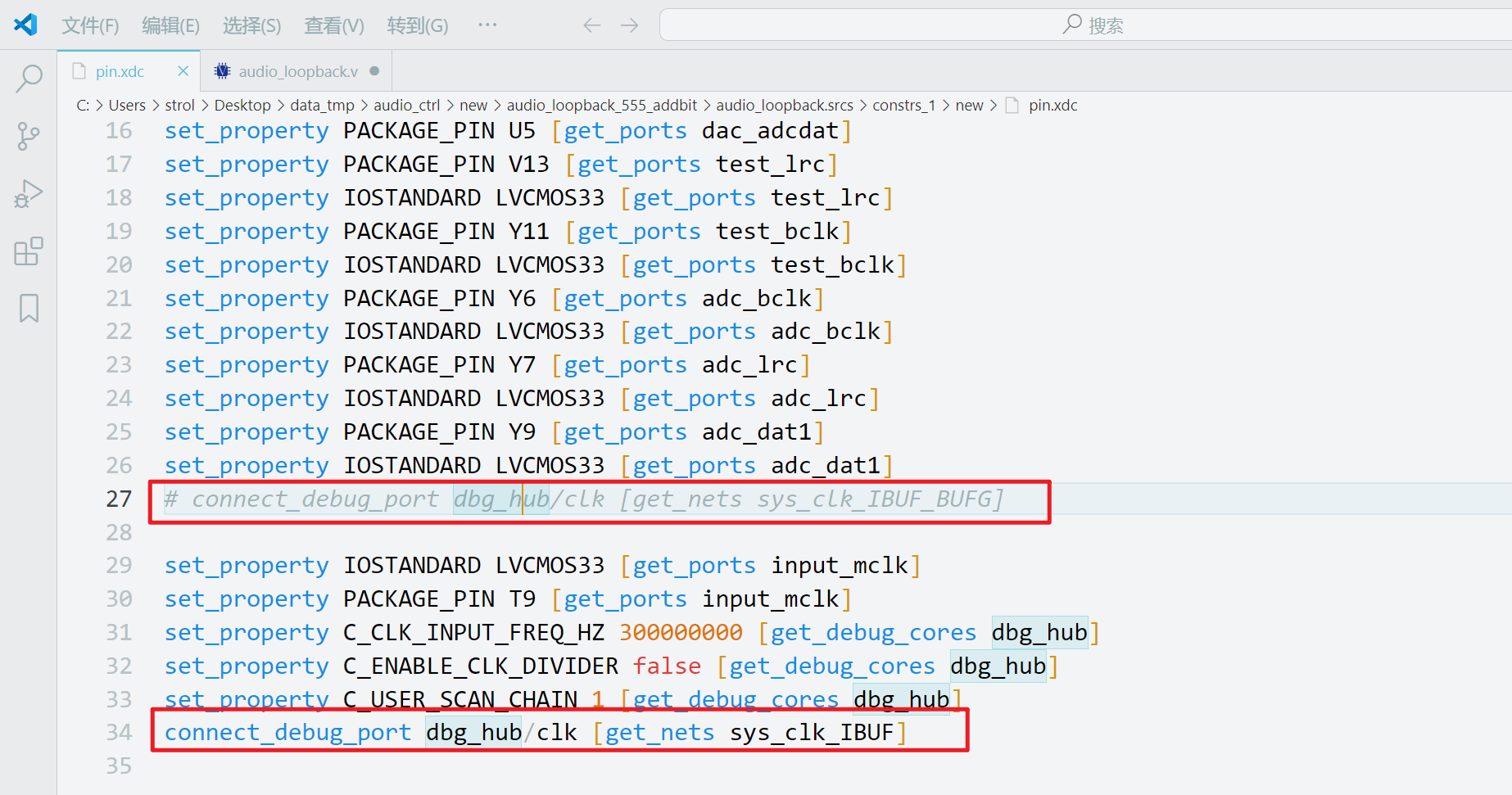

4. Invalid option value specified for ‘-nets‘

出现这种问题的原因是ILA更新了,但是约束没有自动更新,导致找不着dbg_hub的时钟,而这种时钟名是软件生成的,每次都不一样,可以在XDC文件中注释或删除掉dbg_hub的相约束。

然后implement下打开IO,再然后取消一个IO的锁定并重新勾上之后按CTRL+S保存,这时会生成新的约束,如下图,然后重新编译工程~

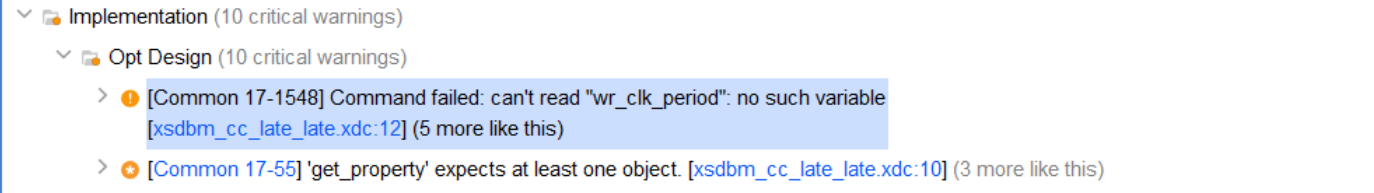

5. [Common 17-1548] Command failed: can’t read “wr_clk_period”: no such variable

- 出现原因:因为Ila中检测的某些信号,时钟频率可能高于ila的clk,只有使用ila或system ila选择native时才可能会出现这种错误,

-

- 解决方法:在.xdc中添加

create_clock -period 16 -name clk -add [get_ports clk_0],其中,clk_0是外部时钟,clk是ila的时钟。16ns是ila检测信号中最高时钟频率的周期数,即ila的时钟接连到检测信号中最高的时钟频率。

- 解决方法:在.xdc中添加

免责声明:我们致力于保护作者版权,注重分享,被刊用文章因无法核实真实出处,未能及时与作者取得联系,或有版权异议的,请联系管理员,我们会立即处理! 部分文章是来自自研大数据AI进行生成,内容摘自(百度百科,百度知道,头条百科,中国民法典,刑法,牛津词典,新华词典,汉语词典,国家院校,科普平台)等数据,内容仅供学习参考,不准确地方联系删除处理! 图片声明:本站部分配图来自人工智能系统AI生成,觅知网授权图片,PxHere摄影无版权图库和百度,360,搜狗等多加搜索引擎自动关键词搜索配图,如有侵权的图片,请第一时间联系我们,邮箱:ciyunidc@ciyunshuju.com。本站只作为美观性配图使用,无任何非法侵犯第三方意图,一切解释权归图片著作权方,本站不承担任何责任。如有恶意碰瓷者,必当奉陪到底严惩不贷!