LPDDR4硬件详解

-

目录

2 LPDDR4颗粒介绍

2.1.LPDDR4架构

3.LPDDR4电气特性

3.1 上电时序

3.2 上电初始化时序

3.3 复位时序

3.4 下电时序

3.5 经典的核心时序

3.6 DMI

3.7 ODT

3.8 ZQ校准

3.8 Vref

4.测量指标

4.1 CLK

4.2 Cammand & address

4.3 DQS write

4.4 DQ write

4.5 DQ read

4.6 ODT-RESET-CKE

2.1测试前准备

2.1.1示波器的选择及设置

2.1.2测试注意事项

2.2信号测试

2.2.1读写分离方法

2.2.2信号测试的内容

DDR基础知识

1.1什么是DDR?

DDR SDRAM全称为Double Data Rate SDRAM,中文名为“双倍数据率SDRAM”。

DDR是在原有的SDRAM的基础上改进而来,严格的说DDR应该叫DDR SDRAM,人们习惯称为DDR。

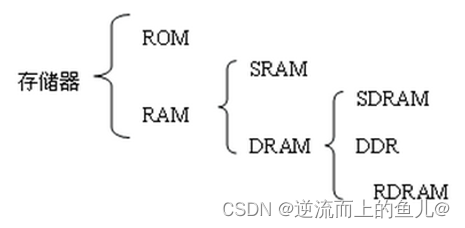

ROM和RAM都是半导体存储器

ROM-Read-Only Memory,是一种只能读出事先所存数据的固态半导体存储器,其特性是一旦储存资料就无法再将之改变或删除

RAM-Random Access Memory,随机是指数据不是线性依次存储,而是自由指定地址进行数据读写,通俗来说就是可以以任何顺序访问,而不管前一次访问的是哪一个位置。

RAM又分两大类,一种称为静态RAM(Static RAM/SRAM),是一种具有静止存取功能的内存,不需要刷新电路即能保存它内部存储的数据,也就是说加电情况下,不需要刷新,数据不会丢失。SRAM速度非常快,是早期读写最快的存储设备了,但是SRAM也有它的缺点,即它的集成度较低,相同容量的内存需要很大的体积,且功耗较大;同时它也非常昂贵,所以只在要求很苛刻的地方使用,譬如CPU的一级缓存,二级缓存。

另一种称为动态RAM(Dynamic RAM/DRAM),DRAM 只能将数据保持很短的时间,为了保持数据,DRAM使用电容存储,所以必须隔一段时间刷新(refresh)一次,如果存储单元没有被刷新,存储的信息就会丢失(关机就会丢失数据);它的速度也比SRAM慢,不过它还是比任何的ROM都要快,但从价格上来说DRAM相比SRAM要便宜很多,计算机内存就是DRAM的。

SDRAM又是在DRAM的基础上发展而来,同时也是属于DRAM中的一种。SDRAM即Synchronous DRAM,同步动态随机存储器,同步是指 Memory工作需要同步时钟,内部命令的发送与数据的传输都以它为基准;

DDR SDRAM又是在SDRAM的基础上发展而来,这种改进型的DRAM和SDRAM是基本一样的,不同之处在于它可以在一个时钟读写两次数据,这样就使得数据传输速度加倍了。

-

- DDR演进路线

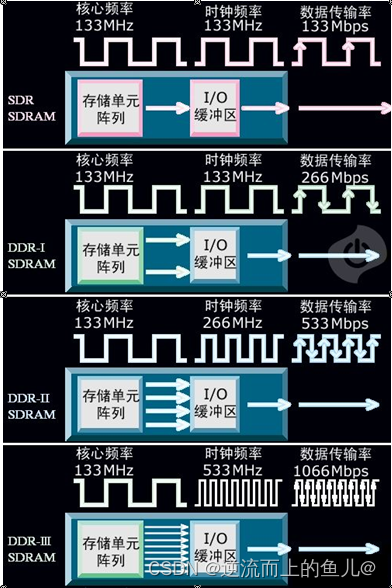

1.3历代DDR提升速率的方法

从SDR SDRAM到DDR3

1.核心频率基本不变,133MHz

2.采用时钟双边沿采样,得到双倍速率

3.通过提升预取位数,提升时钟频率(从1n到8n)

DDR4和DDR3一样,只有8n的prefetch,但为了提升前端Front End的总线速度,不得不在核心频率上动起了手脚,核心频率从200-400MHz,总线速度提升。

比如,我们产品上使用的LPDDR4,在JDDEC上可以看到,使用16为prefetch,对应有533MHz~4266MHz。我们使用的4266Mbps,其存储阵列核心频率就是4266/16=255.625MHz,DDR接口时钟频率为2133MHz

2 LPDDR4颗粒介绍

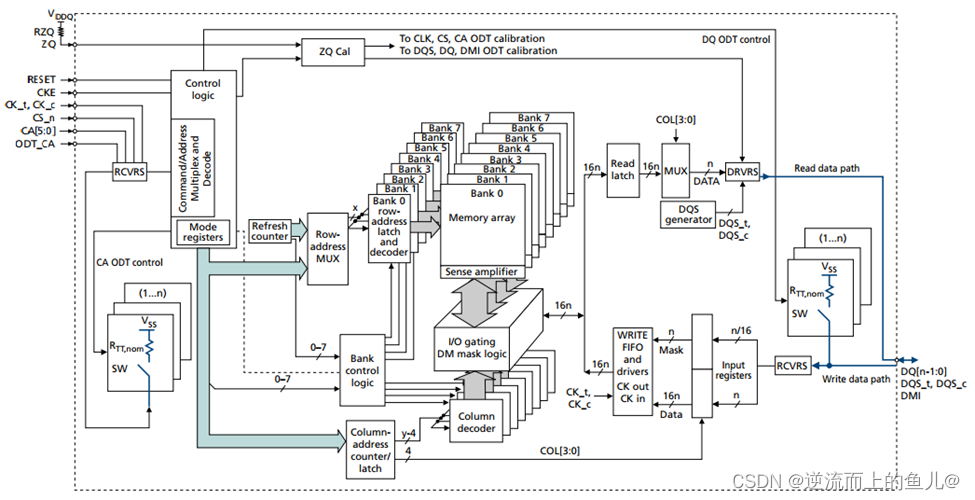

2.1.LPDDR4架构

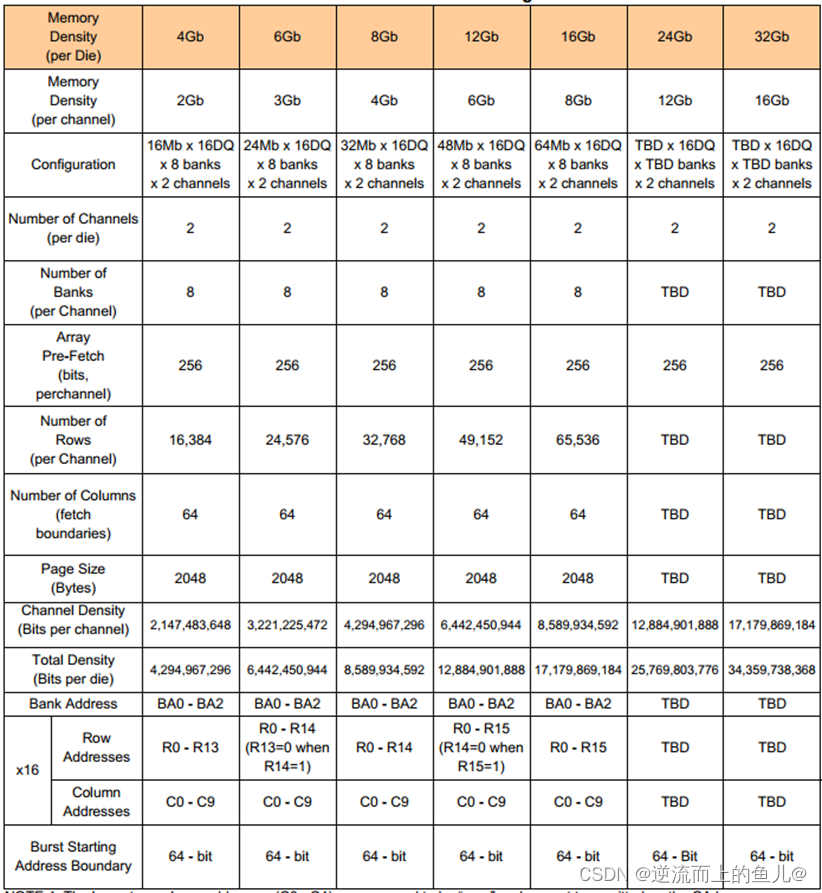

LPDDR4采用了全新的双通道设计,每个裸片包含两个Channnel,每个Channel包含8个Bank,16Bit位宽,16n预读取(DDR4的2倍),每个Die的最高存储容量可以达到32Gb。

对于标准的容量的LPDDR4器件,每个Channel的列是固定的(Page页是固定的),容量越大,行越多。如下图所示:

具体的结构图如下:

那么,如何组成所谓的single-channel/single-rank, dual-channel/single-rank, dual-channel/dual-rank等形形色色的类型颗粒呢?

Rank和channel的概念相信大家都比较清楚,在这里简单的解释一下。所谓channel,可以理解为一个独立的DDR控制器通道,可以独立的控制接在上面的ddr颗粒工作。Rangk,可以理解为通过片选信号,让多组DDR颗粒通过CS片选来分时复用同一个channel。

所以,扩展channle可以扩展DDR的总带宽,阔展Rank可以在相同的channle下扩展内存容量。假设,一颗有两channel,32位宽的cpu,想要获得高带宽,就需要使用dual-channel的颗粒,或者2个16位宽颗粒组成dual-channel,或者4颗8位宽颗粒组成dual-channel;想要在channel满配的情况下,继续宽展容量,就需要去堆rank了。

那么,如何连接扩展呢?

如下图的例子,是4个16位宽die组成dual-rank、dual-channel的架构。工作时,上面两个die或者下面两个die,组成一个rank同时进入读写操作,把16位宽的die扩展成32位宽的一个rank。上下两个rank通过cs片选分时复用,组成一个双rank的组合。

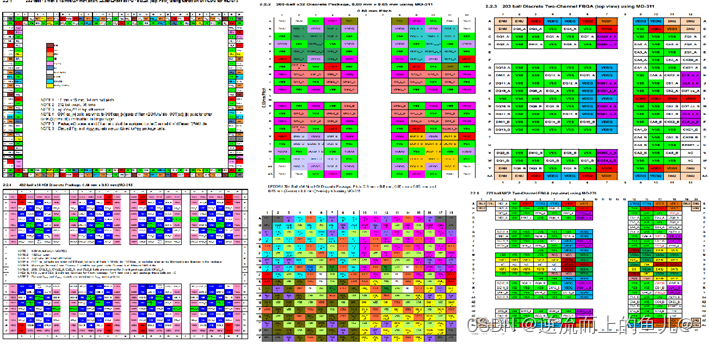

2.2 LPDDR4颗粒封装

在JEDEC上定义了6中封装:

1.272 ball的4通道FBGA封装

2.200 ball的兼容单双通道FBGA封装

3.203 ball的双通道FBGA封装

4.432 ball的HDI封装

5.324 ball的非HDI封装

6.275 ball的MCP封装

2.3 DDR4颗粒的管脚定义

这个比较简单,附一张jedec的介绍图片

需要说明的是,在上面2.1架构上面介绍行列地址的时候,大家可能就会有疑问,为什么只有ca0~ca5六根地址线,却可以识别出多达16个行地址和10个列地址?

答案是位宽不够、周期来凑。首先,LPDDR4同样在DQ和DM使用DDR采样,命令线SDR采样。为了减少命令线的数量,ddr采用了多个时钟周期来传输一个命令,在jedec上定义了1、2、4个时钟周期的命令行。通过多个时钟周期来传递一条指令,从而达到减小ca信号线数量的目的。

3.LPDDR4电气特性

3.1 上电时序

1.上电前,reset保持低;

2.上电时序是VDD1 >= VDD2 >= (VDDQ-200mv)

3. 所有电源在20ms内上电

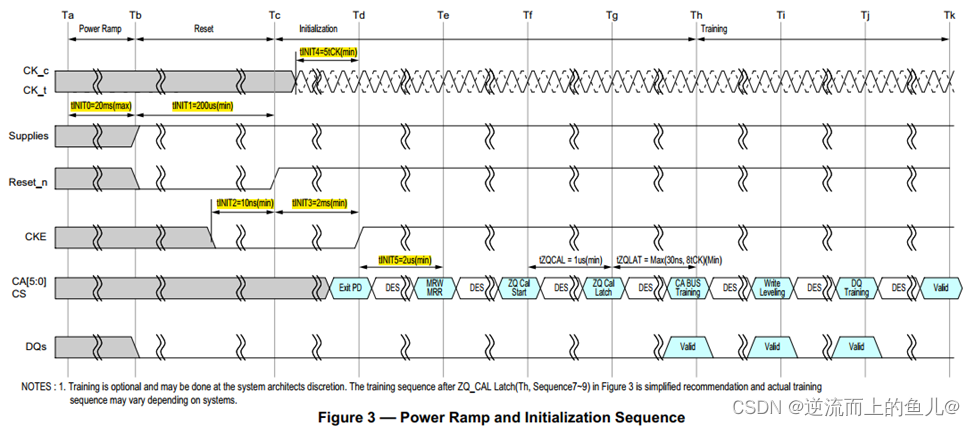

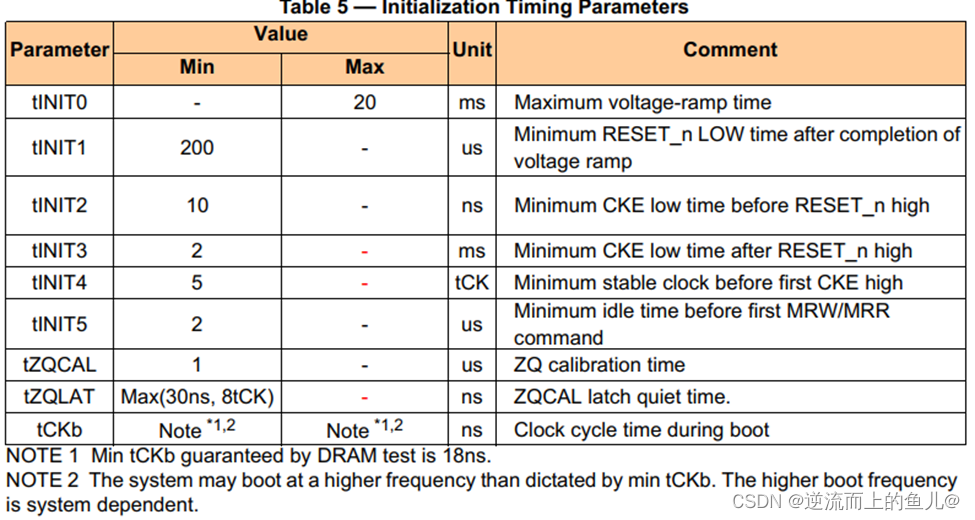

3.2 上电初始化时序

LPDDR4初始化有比较经典的几个时序需要测量,具体参考图和测试指标,在jedec上面有非常直观的给出,设计电源和控制器必须满足这个要求:

另外,在初始化过程中,为了防止DDR的功能异常。此时,一些重要的延时参数和ODT、vref采用默认值,默认值如下:

3.3 复位时序

- reset低电平信号质量满足= VDD2 >= (VDDQ-200mv)

最长下电时间